- 您现在的位置:买卖IC网 > Sheet目录1991 > CS4397-KSZ (Cirrus Logic Inc)IC DAC 24BIT MULTY STNDRD 28SOIC

CS4397

16

DS333F1

3.0 REGISTER DESCRIPTION

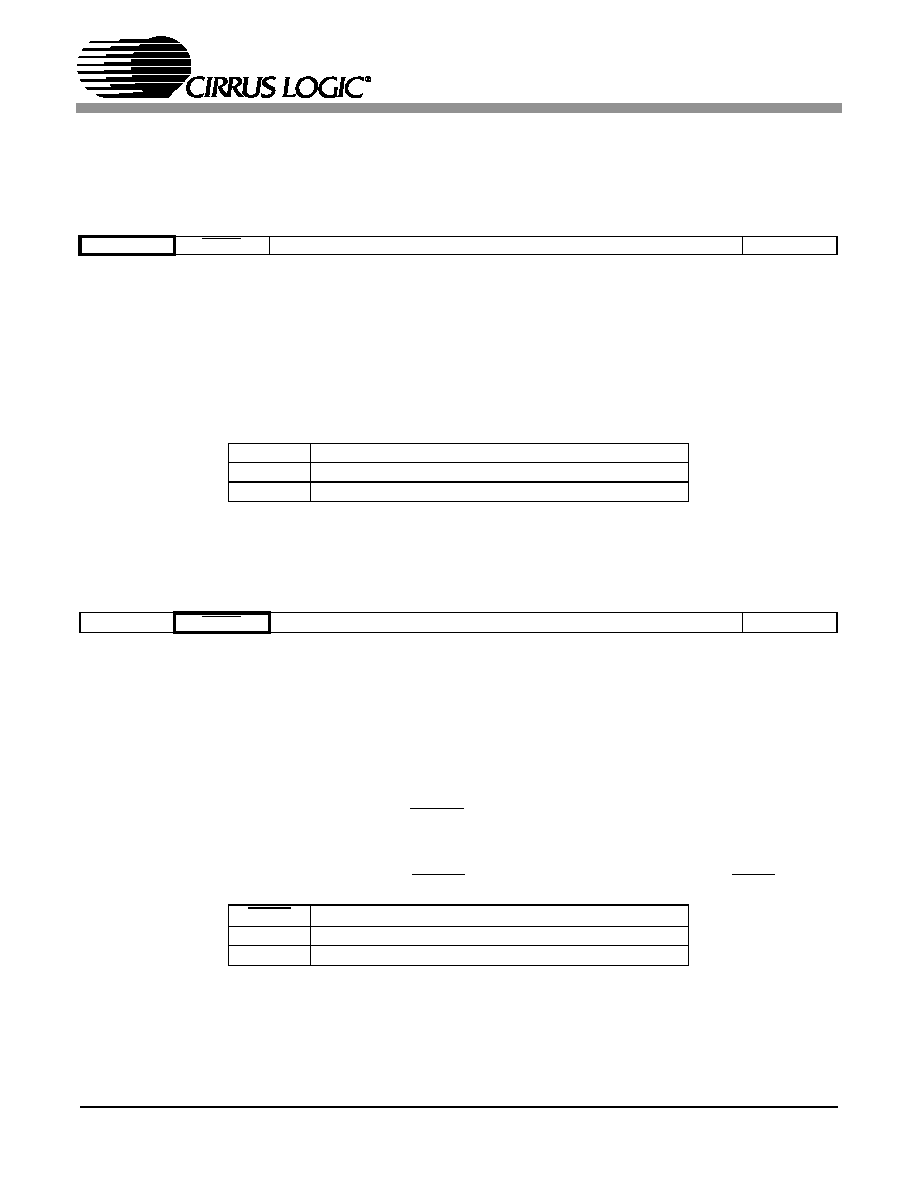

3.1 DIFFERENTIAL DC OFFSET CALIBRATION

Mode Control Register (address 01h)

Access:

R/W in I2C and SPI.

Default:

0 - Disabled

Function:

Enabling this function will initiate a calibration to minimize the differential DC offset. This function will be

automatically reset following completion of the calibration sequence.

3.2 SOFT MUTE

Mode Control Register (address 01h)

Access:

R/W in I2C and SPI.

Default:

0 - Enabled

Function:

The analog outputs will ramp to a muted state when enabled. The ramp requires 1152 left/right clock cy-

cles in Single Speed, 2304 cycles in Double Speed and 4608 cycles in Quad Speed mode. The bias volt-

age on the outputs will be retained and MUTEC will go low at the completion of the ramp period.

The analog outputs will ramp to a normal state when this function transitions from the enabled to disabled

state. The ramp requires 1152 left/right clock cycles in Single Speed, 2304 cycles in Double Speed and

4608 cycles in Quad Speed mode. The MUTEC will go high immediately on disabling of MUTE.

76543

210

CAL

MUTE

M4

M3

M2

M1

M0

PDN

CAL

MODE

0

Disabled : CAL complete

1

Enabled : CAL initiated

Table 1.

76543

210

CAL

MUTE

M4

M3

M2

M1

M0

PDN

MUTE

MODE

0

Enabled

1

Disabled

Table 2.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4398-CZZ

IC DAC 120DB 192KHZ W/VC 28TSSOP

CS43L22-CNZR

IC DAC W/HDPN & SPKR AMPS 40-QFN

CS4461-CZZR

IC ADC PSR FEEDBACK 24-TSSOP

CS5340-CZZ

IC ADC AUD 101DB 200KHZ 16-TSSOP

CS5340-DZZR

IC ADC AUD 101DB 200KHZ 16-TSSOP

CS5341-DZZ

IC ADC AUD 105DB 200KHZ 16-TSSOP

CS5342-CZZ

IC ADC AUD 105DB 200KHZ 16-TSSOP

CS5345-CQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

相关代理商/技术参数

CS4397-KSZR

功能描述:数模转换器- DAC IC 24Bit 192 kHz DAC for Digital Audio RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4398

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:120 dB, 192 kHz Multi-Bit DAC with Volume Control

CS4398-CZZ

功能描述:音频数/模转换器 IC Stereo Multi-Bit DAC 192kHz 120dB w/VC RoHS:否 制造商:Texas Instruments 转换器数量: 分辨率:16 bit 接口类型:I2S, UBS 转换速率: 信噪比:98 dB 工作电源电压:5 V DAC 输出端数量:2 工作温度范围:- 25 C to + 85 C 电源电流:23 mA 安装风格:SMD/SMT 封装 / 箱体:TQFP-32 封装:Reel

CS4398-CZZR

功能描述:数模转换器- DAC IC 120dB 192kHz Mlt-Bt DAC w/Volctrl RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS4399-CNZ

功能描述:HIPRFDACINTGHPDRIVR&IMPED DETCTN 制造商:cirrus logic inc. 系列:* 包装:托盘 零件状态:在售 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商器件封装:40-QFN(5x5) 标准包装:490

CS4399-CNZR

功能描述:HIPRFDACINTGHPDRIVR&IMPED DETCTN 制造商:cirrus logic inc. 系列:* 包装:剪切带(CT) 零件状态:在售 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商器件封装:40-QFN(5x5) 标准包装:1

CS4399-CWZR

功能描述:HIPRFDACINTGHPDRIVR&IMPED DETCTN 制造商:cirrus logic inc. 系列:* 包装:剪切带(CT) 零件状态:在售 安装类型:表面贴装 封装/外壳:42-UFBGA,WLCSP 供应商器件封装:42-WLCSP 标准包装:1

CS43L21

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Power, Stereo Digital to Analog Converter